444 Alaska Avenue

Suite #BAA205 Torrance, CA 90503 USA

+1 424 999 9627

24/7 Customer Support

sales@markwideresearch.com

Email us at

Suite #BAA205 Torrance, CA 90503 USA

24/7 Customer Support

Email us at

Corporate User License

Unlimited User Access, Post-Sale Support, Free Updates, Reports in English & Major Languages, and more

$2450

The China EDA Electronic Design Automation market represents one of the most dynamic and rapidly evolving sectors within the country’s semiconductor and electronics ecosystem. Electronic Design Automation tools have become indispensable for designing complex integrated circuits, printed circuit boards, and electronic systems that power everything from smartphones to automotive electronics. China’s strategic focus on semiconductor self-sufficiency has significantly accelerated demand for advanced EDA solutions, creating unprecedented opportunities for both domestic and international providers.

Market dynamics in China’s EDA sector are characterized by strong government support, increasing domestic chip design capabilities, and growing investments in research and development. The market has experienced remarkable growth, with adoption rates increasing by approximately 23% annually as Chinese semiconductor companies expand their design capabilities. Government initiatives such as the National Integrated Circuit Industry Development Guidelines have provided substantial backing for EDA tool development and deployment across various industry segments.

Technological advancement remains a key driver, with artificial intelligence integration, cloud-based solutions, and advanced process node support becoming critical differentiators. The market encompasses various segments including analog design, digital design, verification tools, and manufacturing-oriented solutions, each experiencing distinct growth patterns and competitive dynamics.

The China EDA Electronic Design Automation market refers to the comprehensive ecosystem of software tools, methodologies, and services used for designing, verifying, and manufacturing electronic systems and integrated circuits within the Chinese market. EDA tools enable engineers to create complex semiconductor designs through automated processes that would be impossible to accomplish manually, encompassing everything from initial concept to final manufacturing preparation.

Electronic Design Automation encompasses multiple categories of software solutions including schematic capture, simulation, layout design, verification, and test generation tools. These solutions enable Chinese semiconductor companies, electronics manufacturers, and research institutions to develop cutting-edge products ranging from consumer electronics to advanced computing systems. The market includes both commercial EDA software licenses and emerging open-source alternatives that are gaining traction among Chinese developers.

Strategic importance of the EDA market extends beyond mere software licensing, representing China’s broader ambitions for technological independence and semiconductor manufacturing capabilities. The market includes professional services, training, and support infrastructure that enables Chinese companies to effectively utilize these sophisticated design tools.

China’s EDA market stands at a critical juncture, driven by unprecedented demand for semiconductor design capabilities and supported by comprehensive government policies promoting domestic technology development. The market has demonstrated exceptional resilience and growth potential, with Chinese companies increasingly investing in advanced design automation tools to compete globally. Market penetration has reached significant levels across major industry segments, with particularly strong adoption in consumer electronics and telecommunications sectors.

Key market characteristics include rapid technological evolution, increasing localization efforts, and growing emphasis on AI-powered design tools. Chinese EDA companies have made substantial progress in developing competitive solutions, while international providers continue to maintain strong market positions through advanced technology offerings. The market benefits from robust venture capital investment, with funding for EDA startups increasing by approximately 35% year-over-year.

Competitive landscape features a mix of established international players and emerging Chinese companies, creating a dynamic environment that fosters innovation and technological advancement. The market’s future trajectory appears highly promising, supported by China’s commitment to semiconductor independence and the growing complexity of electronic designs requiring sophisticated automation tools.

Strategic insights reveal several critical trends shaping China’s EDA market landscape:

Market maturation indicators suggest that China’s EDA sector is transitioning from primarily consuming international solutions to developing indigenous capabilities that can compete on both domestic and global stages.

Primary growth drivers propelling China’s EDA market include the country’s strategic semiconductor development initiatives and increasing complexity of electronic designs. Government policies such as the “Made in China 2025” strategy have created substantial demand for domestic EDA capabilities, with state-backed funding supporting both tool development and adoption across various industry sectors.

Technological complexity represents another fundamental driver, as modern semiconductor designs require sophisticated automation tools to manage millions of transistors and complex interconnections. The shift toward advanced process nodes, including 7nm and 5nm technologies, has created urgent demand for EDA tools capable of handling these challenging design requirements. Design productivity pressures continue to intensify as companies seek to reduce development cycles while maintaining high quality standards.

Market expansion in emerging applications such as artificial intelligence chips, Internet of Things devices, and automotive electronics has created new categories of design challenges requiring specialized EDA solutions. The growing emphasis on system-level design and verification has expanded the scope of EDA tools beyond traditional integrated circuit design to encompass entire electronic systems.

Investment momentum from both private and public sources has accelerated EDA tool development, with venture capital funding for Chinese EDA startups reaching record levels and demonstrating strong confidence in the sector’s growth potential.

Significant challenges facing China’s EDA market include the high complexity and cost associated with developing competitive design automation tools. Technical barriers remain substantial, as creating EDA software requires deep expertise in semiconductor physics, advanced algorithms, and software engineering, creating lengthy development cycles and high investment requirements.

International competition presents ongoing challenges, with established global EDA providers maintaining technological advantages in certain specialized areas such as advanced analog design and cutting-edge process node support. Talent shortage represents a critical constraint, as the specialized skills required for EDA development and application remain scarce within the Chinese market.

Intellectual property concerns and potential technology transfer restrictions create uncertainty for both domestic and international companies operating in the Chinese EDA market. Standardization challenges arise as different EDA tools may use incompatible formats and methodologies, creating integration difficulties for design teams.

Market fragmentation occurs as numerous smaller EDA companies compete for market share, potentially leading to resource dispersion and reduced economies of scale. The high cost of EDA tool licenses can also limit adoption among smaller Chinese companies and startups, creating barriers to market expansion.

Substantial opportunities exist within China’s EDA market, particularly in developing specialized tools for emerging applications such as artificial intelligence accelerators and quantum computing systems. Localization advantages present significant potential for Chinese EDA companies to provide better customer support, customized features, and competitive pricing compared to international alternatives.

Cloud-based solutions offer tremendous growth potential, enabling smaller companies to access sophisticated EDA tools without substantial upfront investments while providing scalability for larger enterprises. AI-powered design automation represents a frontier opportunity, with machine learning techniques potentially revolutionizing how electronic systems are designed and optimized.

Educational partnerships with Chinese universities and research institutions create opportunities to develop the next generation of EDA users and developers while fostering innovation in design methodologies. Vertical integration opportunities exist for EDA companies to develop specialized solutions for specific industries such as automotive, telecommunications, or consumer electronics.

Open-source initiatives present opportunities to build collaborative development communities and reduce barriers to EDA tool adoption. The growing emphasis on system-level design creates opportunities for tools that can handle complex multi-domain simulations and optimizations across electrical, mechanical, and software domains.

Dynamic interactions within China’s EDA market reflect the complex interplay between government policy, technological advancement, and competitive pressures. Policy influence remains particularly strong, with government initiatives directly impacting investment flows, research priorities, and market adoption patterns. The market demonstrates cyclical characteristics aligned with semiconductor industry investment cycles and product development timelines.

Competitive dynamics are intensifying as Chinese companies develop increasingly sophisticated EDA solutions while international providers adapt their strategies for the Chinese market. Technology transfer and collaboration patterns continue evolving, with some international companies establishing research and development centers in China to better serve local customers and access Chinese talent.

Customer behavior is shifting toward more strategic EDA tool selection, with Chinese companies increasingly evaluating total cost of ownership, long-term support capabilities, and alignment with domestic technology strategies. Innovation cycles are accelerating, with new EDA capabilities being developed and deployed more rapidly than in previous decades.

Market consolidation trends are emerging as successful EDA companies acquire complementary technologies and smaller competitors to build comprehensive solution portfolios. According to MarkWide Research analysis, market concentration has increased by approximately 18% over the past three years as leading companies expand their capabilities through strategic acquisitions.

Comprehensive research approach employed for analyzing China’s EDA market combines quantitative data analysis with qualitative insights from industry experts, government officials, and technology practitioners. Primary research includes extensive interviews with EDA company executives, semiconductor design engineers, and academic researchers to understand market trends, challenges, and opportunities.

Secondary research encompasses analysis of government policy documents, industry reports, patent filings, and financial disclosures from publicly traded EDA companies operating in China. Market sizing methodologies utilize multiple approaches including top-down analysis based on semiconductor industry spending patterns and bottom-up analysis based on EDA tool licensing and usage data.

Data validation processes ensure accuracy through cross-referencing multiple sources, expert review panels, and statistical verification techniques. Trend analysis incorporates historical data spanning multiple years to identify sustainable growth patterns and cyclical variations within the market.

Regional analysis methodology accounts for variations in EDA adoption across different Chinese provinces and cities, considering factors such as local semiconductor industry concentration, government support levels, and educational infrastructure. Competitive intelligence gathering includes analysis of company strategies, product portfolios, and market positioning across both domestic and international EDA providers.

Geographic distribution of China’s EDA market shows significant concentration in major technology hubs, with the Beijing-Tianjin-Hebei region, Yangtze River Delta, and Pearl River Delta accounting for approximately 78% of total market activity. Beijing maintains its position as the primary center for EDA research and development, hosting numerous domestic EDA companies and international research centers.

Shanghai and surrounding areas demonstrate strong EDA adoption driven by the concentration of semiconductor manufacturing facilities and design houses. The region benefits from proximity to major foundries and assembly facilities, creating integrated ecosystems that support comprehensive EDA tool deployment. Shenzhen continues to be a major hub for EDA applications in consumer electronics and telecommunications equipment design.

Emerging regional centers including Xi’an, Chengdu, and Wuhan are developing significant EDA capabilities supported by local government initiatives and university partnerships. These regions offer cost advantages and access to technical talent, attracting both domestic and international EDA companies to establish operations.

Regional specialization patterns are emerging, with certain areas focusing on specific EDA applications such as analog design tools, digital verification solutions, or manufacturing-oriented software. Government support varies by region, with some provinces offering particularly attractive incentives for EDA company establishment and expansion.

Market leadership in China’s EDA sector features a dynamic mix of international technology giants and emerging domestic companies, creating a competitive environment that drives continuous innovation and technological advancement.

Competitive strategies vary significantly, with international companies emphasizing technological leadership and comprehensive solution portfolios, while Chinese companies focus on localization advantages, competitive pricing, and specialized market segments. Partnership approaches are becoming increasingly important as companies seek to combine complementary strengths and access new market opportunities.

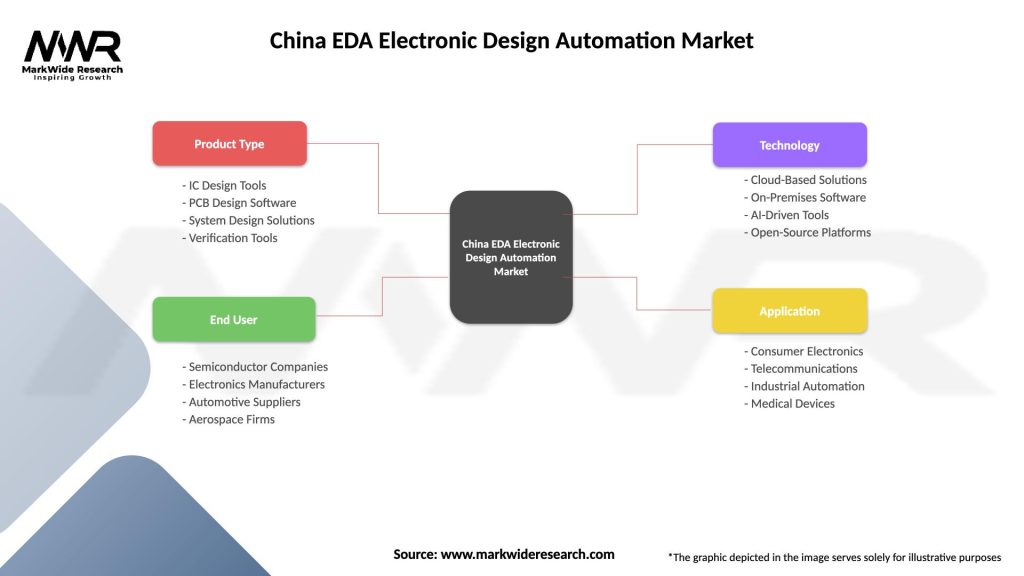

Market segmentation analysis reveals distinct categories within China’s EDA market, each characterized by unique growth patterns, competitive dynamics, and customer requirements.

By Product Type:

By Application:

By End-User Industry:

Digital design tools represent the largest category within China’s EDA market, driven by the predominance of digital integrated circuits in consumer electronics and computing applications. This segment benefits from mature algorithms and established methodologies, enabling Chinese companies to develop competitive solutions more readily than in other EDA categories. Market share for digital tools accounts for approximately 42% of total EDA adoption across Chinese companies.

Analog and mixed-signal design tools present greater technical challenges but offer significant opportunities for differentiation and higher margins. Chinese EDA companies are making substantial investments in this category, recognizing its strategic importance for advanced semiconductor designs. Growth rates in analog EDA tools are exceeding overall market growth by approximately 15% annually.

Verification and validation tools are experiencing rapid growth as design complexity increases and quality requirements become more stringent. This category benefits from AI integration opportunities and cloud-based deployment models that reduce infrastructure requirements for users. Cloud adoption in verification tools has reached approximately 28% among Chinese companies.

System-level design tools represent an emerging category with substantial growth potential, addressing the need for multi-domain simulation and optimization across electrical, mechanical, and software components. This category aligns well with China’s emphasis on complete system design capabilities rather than just component-level tools.

Semiconductor companies benefit from advanced EDA tools through significantly reduced design cycles, improved design quality, and enhanced ability to explore complex design spaces. Design productivity improvements of up to 40% are achievable through effective EDA tool deployment, enabling faster time-to-market for new products and improved competitive positioning.

EDA tool providers gain access to one of the world’s largest and fastest-growing markets for design automation solutions. The Chinese market offers opportunities for both premium technology solutions and cost-effective alternatives, enabling different competitive strategies and market positioning approaches. Revenue growth potential in the Chinese market significantly exceeds global averages for most EDA categories.

Government stakeholders achieve strategic objectives related to semiconductor independence and technological capability development through EDA market growth. Economic benefits include job creation in high-value technology sectors, increased innovation capacity, and reduced dependence on foreign technology suppliers.

Academic institutions benefit from improved access to advanced design tools for research and education purposes, enabling better preparation of students for careers in semiconductor and electronics industries. Research collaboration opportunities with EDA companies provide additional funding sources and practical application outlets for academic research.

Investment community gains access to high-growth opportunities in a strategically important technology sector, with potential for significant returns as Chinese EDA companies develop competitive capabilities and expand market share.

Strengths:

Weaknesses:

Opportunities:

Threats:

Artificial intelligence integration represents the most significant trend transforming China’s EDA market, with machine learning algorithms being incorporated into design optimization, verification acceleration, and automated debugging processes. AI-powered tools are demonstrating substantial productivity improvements and enabling design teams to tackle increasingly complex challenges with greater efficiency.

Cloud-based deployment models are gaining rapid adoption as companies seek to reduce infrastructure costs and improve scalability. Cloud EDA platforms enable smaller companies to access sophisticated tools while providing larger enterprises with elastic computing resources for peak design activities. This trend is particularly important in China where many emerging semiconductor companies prefer operational expense models over large capital investments.

Open-source EDA initiatives are developing momentum as Chinese companies and research institutions collaborate on developing alternative solutions to commercial tools. These initiatives aim to reduce dependence on foreign EDA suppliers while fostering innovation through collaborative development approaches. Community participation in open-source EDA projects has grown by approximately 52% over the past two years.

System-level design emphasis is increasing as electronic products become more complex and require optimization across multiple domains including electrical, mechanical, thermal, and software components. This trend creates opportunities for EDA tools that can handle multi-physics simulations and system-level optimization challenges.

Specialized vertical solutions are emerging as EDA companies develop tools tailored for specific applications such as automotive electronics, IoT devices, or artificial intelligence accelerators, providing competitive advantages through domain expertise and optimized workflows.

Strategic partnerships between Chinese semiconductor companies and EDA providers have intensified, with several major collaborations announced focusing on advanced process node support and specialized design methodologies. These partnerships often include joint development programs and technology transfer agreements that benefit both parties through shared expertise and market access.

Government funding initiatives have provided substantial support for domestic EDA development, with several billion-dollar investment programs launched to accelerate Chinese EDA capabilities. These initiatives include direct company funding, research grants, and infrastructure development programs that strengthen the overall EDA ecosystem.

Acquisition activity has increased as successful EDA companies seek to expand their capabilities through strategic purchases of complementary technologies and smaller competitors. MWR data indicates that EDA-related acquisitions in China have grown by approximately 31% compared to the previous year, reflecting industry consolidation trends.

International expansion efforts by Chinese EDA companies are beginning to emerge, with several domestic providers establishing operations in other Asian markets and exploring opportunities in Europe and North America. These expansion efforts demonstrate growing confidence in Chinese EDA technology capabilities.

Educational partnerships between EDA companies and Chinese universities have expanded significantly, with comprehensive programs established for student training, faculty development, and collaborative research projects that strengthen the talent pipeline for the industry.

Strategic recommendations for EDA companies operating in China emphasize the importance of balancing technological advancement with market localization requirements. International providers should consider establishing stronger local presence through research and development centers, customer support facilities, and partnership programs with Chinese companies and institutions.

Chinese EDA companies should focus on developing specialized capabilities in specific market segments rather than attempting to compete across all EDA categories simultaneously. Vertical specialization strategies can provide competitive advantages and enable more effective resource allocation for technology development and market penetration.

Investment strategies should prioritize companies with strong intellectual property portfolios, experienced development teams, and clear market differentiation strategies. Due diligence processes should carefully evaluate technical capabilities, customer relationships, and long-term sustainability of business models in the competitive EDA landscape.

Market entry strategies for new participants should consider partnership approaches with established players rather than independent market entry, given the complexity of EDA technology development and the importance of customer relationships in this sector. Collaborative approaches can accelerate market penetration while reducing development risks and costs.

Technology development priorities should align with emerging market trends such as AI integration, cloud deployment, and system-level design capabilities. Companies that successfully incorporate these trends into their product roadmaps are likely to achieve stronger competitive positions and growth prospects.

Long-term prospects for China’s EDA market remain exceptionally positive, driven by the country’s strategic commitment to semiconductor independence and the continuing growth of domestic electronics industries. Market expansion is expected to continue at robust rates, with growth projections indicating sustained double-digit increases over the next five years.

Technological evolution will likely accelerate as Chinese EDA companies mature and develop increasingly sophisticated capabilities. Innovation cycles are expected to shorten as competition intensifies and customer demands for advanced features increase. The integration of artificial intelligence and machine learning into EDA tools will become standard rather than exceptional, fundamentally changing how electronic designs are created and optimized.

Market structure evolution will likely result in greater consolidation as successful companies acquire complementary technologies and smaller competitors. This consolidation process should create stronger Chinese EDA companies capable of competing more effectively with international providers while offering comprehensive solution portfolios.

International competitiveness of Chinese EDA companies is expected to improve significantly, with several domestic providers likely to achieve global market recognition and expansion opportunities. According to MarkWide Research projections, Chinese EDA companies could capture approximately 25% of the global market share within the next decade through continued technology development and strategic expansion efforts.

Application diversity will continue expanding as new electronic design challenges emerge in areas such as quantum computing, advanced AI accelerators, and next-generation communication systems, creating ongoing opportunities for EDA innovation and market growth.

China’s EDA Electronic Design Automation market represents a critical component of the country’s broader semiconductor and electronics ecosystem, demonstrating remarkable growth potential and strategic importance. The market benefits from strong government support, growing domestic demand, and increasing technological capabilities among Chinese EDA providers. Competitive dynamics continue evolving as domestic companies develop more sophisticated solutions while international providers adapt their strategies for the Chinese market.

Key success factors for market participants include technological innovation, customer relationship management, and strategic positioning within China’s rapidly evolving semiconductor landscape. The market offers substantial opportunities for both established international companies and emerging Chinese providers, with different competitive strategies proving viable across various market segments.

Future growth prospects remain highly favorable, supported by China’s strategic technology initiatives, increasing design complexity requirements, and the continuing expansion of domestic electronics industries. The market is well-positioned to achieve sustained growth while contributing to China’s broader objectives of technological independence and innovation leadership in critical technology sectors.

What is EDA Electronic Design Automation?

EDA Electronic Design Automation refers to software tools used for designing electronic systems such as integrated circuits and printed circuit boards. These tools help engineers automate complex design processes, improving efficiency and accuracy in the development of electronic products.

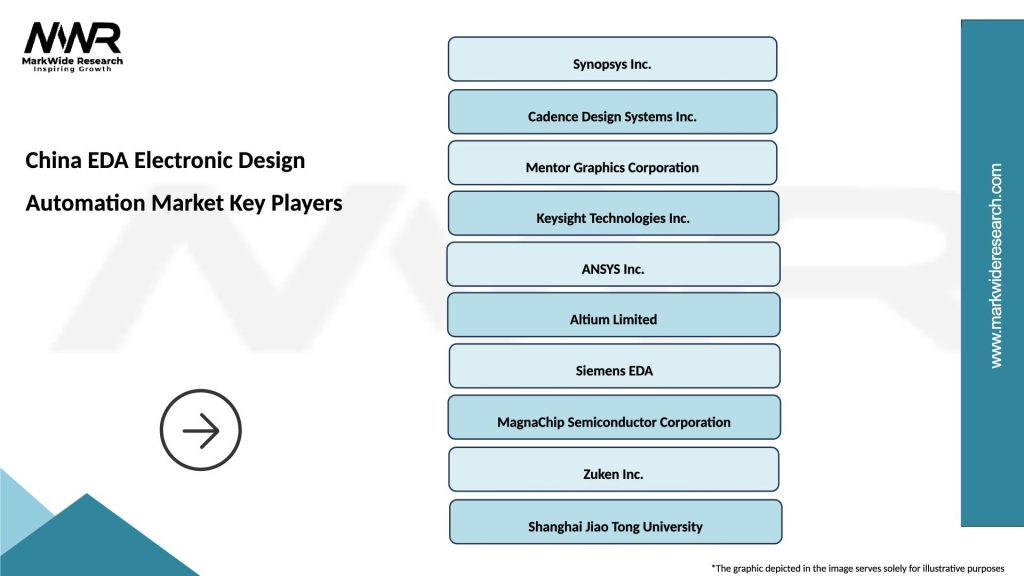

What are the key players in the China EDA Electronic Design Automation Market?

Key players in the China EDA Electronic Design Automation Market include companies like Synopsys, Cadence Design Systems, and Mentor Graphics. These companies provide a range of EDA tools and solutions that cater to various aspects of electronic design, among others.

What are the growth factors driving the China EDA Electronic Design Automation Market?

The growth of the China EDA Electronic Design Automation Market is driven by the increasing demand for advanced electronic devices, the rise of IoT applications, and the need for efficient design processes in semiconductor manufacturing. Additionally, the expansion of the automotive and telecommunications sectors contributes to market growth.

What challenges does the China EDA Electronic Design Automation Market face?

Challenges in the China EDA Electronic Design Automation Market include the high cost of EDA tools, the complexity of integrating new technologies, and the shortage of skilled professionals in electronic design. These factors can hinder the adoption and effective use of EDA solutions.

What opportunities exist in the China EDA Electronic Design Automation Market?

Opportunities in the China EDA Electronic Design Automation Market include the growing demand for AI and machine learning applications in design processes, the expansion of 5G technology, and the increasing focus on energy-efficient designs. These trends present avenues for innovation and growth in the market.

What trends are shaping the China EDA Electronic Design Automation Market?

Trends shaping the China EDA Electronic Design Automation Market include the adoption of cloud-based EDA solutions, the integration of AI in design automation, and the increasing focus on collaborative design environments. These trends are transforming how electronic designs are created and optimized.

China EDA Electronic Design Automation Market

| Segmentation Details | Description |

|---|---|

| Product Type | IC Design Tools, PCB Design Software, System Design Solutions, Verification Tools |

| End User | Semiconductor Companies, Electronics Manufacturers, Automotive Suppliers, Aerospace Firms |

| Technology | Cloud-Based Solutions, On-Premises Software, AI-Driven Tools, Open-Source Platforms |

| Application | Consumer Electronics, Telecommunications, Industrial Automation, Medical Devices |

Please note: The segmentation can be entirely customized to align with our client’s needs.

Leading companies in the China EDA Electronic Design Automation Market

Please note: This is a preliminary list; the final study will feature 18–20 leading companies in this market. The selection of companies in the final report can be customized based on our client’s specific requirements.

Trusted by Global Leaders

Fortune 500 companies, SMEs, and top institutions rely on MWR’s insights to make informed decisions and drive growth.

ISO & IAF Certified

Our certifications reflect a commitment to accuracy, reliability, and high-quality market intelligence trusted worldwide.

Customized Insights

Every report is tailored to your business, offering actionable recommendations to boost growth and competitiveness.

Multi-Language Support

Final reports are delivered in English and major global languages including French, German, Spanish, Italian, Portuguese, Chinese, Japanese, Korean, Arabic, Russian, and more.

Unlimited User Access

Corporate License offers unrestricted access for your entire organization at no extra cost.

Free Company Inclusion

We add 3–4 extra companies of your choice for more relevant competitive analysis — free of charge.

Post-Sale Assistance

Dedicated account managers provide unlimited support, handling queries and customization even after delivery.

GET A FREE SAMPLE REPORT

This free sample study provides a complete overview of the report, including executive summary, market segments, competitive analysis, country level analysis and more.

ISO AND IAF CERTIFIED

GET A FREE SAMPLE REPORT

This free sample study provides a complete overview of the report, including executive summary, market segments, competitive analysis, country level analysis and more.

ISO AND IAF CERTIFIED

Suite #BAA205 Torrance, CA 90503 USA

24/7 Customer Support

Email us at